Złożone pamięci półprzewodnikowe stanowią integralną część większości współczesnych modułów elektronicznych będących składowymi urządzeń technicznych wykorzystywanych w wielu dziedzinach życia. Zjawiskiem codziennym są dziś urządzenia cyfrowe pełniące rolę systemów o znaczeniu krytycznym. Efektem tego jest ciągły wzrost wymagań dotyczących długotrwałej, niezawodnej i często nieprzerwanej pracy, zarówno pojedynczych układów scalonych, pakietów, urządzeń, jak również całych systemów cyfrowych. Z danych statystycznych wynika, że około 70% wszystkich uszkodzeń w systemach cyfrowych spowodowanych jest uszkodzeniami pamięci. Dlatego już na etapie projektowania należy zadbać o możliwość łatwego i efektywnego ich testowania.

Autorzy:

dr inż. Ireneusz Mrozek, prof. dr hab. inż. Vyacheslav Yarmolik

Politechnika Białostocka, Wydział Informatyki

Jednym z najczęściej stosowanych rozwiązań jest projektowanie układów z myślą o testowaniu – DFT (ang. Design For Testability). Z uwagi na coraz większą integrację układów cyfrowych, umieszczaniu wielu modułów (w tym pamięci) na jednym podłożu krzemowym, tradycyjne „zewnętrzne” techniki testowania, nie zawsze mogą być stosowane. Rozwiązaniem problemu okazały się bogato opisane w literaturze techniki testów wbudowanych BIST (ang. Built-In-Self Test) i samonaprawy BISR (ang. Built-In-Self Repair) [1–7].

W procesie wbudowanego testowania pamięci szeroko zaakceptowane zostały testy krokowe (ang. march tests) łączące wysoką wykrywalność uszkodzeń z niską złożonością testu rzędu O (N) [8]. Ponadto klasyczne testy krokowe są łatwo konwertowalne do testów transparentnych (ang. transparent march tests) [9–12]. Testy transparentne umożliwiają zachowanie niezmienionej zawartości pamięci w stosunku do zawartości z momentu rozpoczęcia testu. Dzięki temu są one szczególnie predysponowane do realizacji periodycznych testów wykonywanych w czasie normalnej pracy urządzenia [8]. Jednak wraz ze wzrostem rozmiarów pamięci czas niezbędny na jej przetestowanie ulega również wydłużeniu. Problem ten jest szczególnie widoczny w wypadku testów transparentnych. Przy klasycznym podejściu każdorazowa realizacja testu wymaga dodatkowych nakładów obliczeniowych niezbędnych do wyliczenia sygnatury odniesienia. Złożoność tego procesu sięga około 50% oryginalnej złożoności realizowanego testu [9].

W artykule przedstawiony zostanie transparentny sposób testowania umożliwiający uniknięcie niekorzystnych narzutów czasowych związanych z wyliczaniem sygnatury odniesienia. Wykorzystana zostanie technika SAODC (ang. Self-Adjusting Output Data Compression) zaproponowana oryginalnie do testów nietransparentnych [13]. Okazuje się, iż wykorzystanie powyższej techniki w testowaniu transparentnym pozwala zminimalizować czas niezbędny do wyliczenia sygnatury odniesienia. Tak realizowane testy cechują się tą samą wydajnością co realizacje standardowe, a przy niewielkich modyfikacjach implementacyjnych ich wydajność nawet wzrasta co zostanie potwierdzone wynikami przeprowadzonych badań.

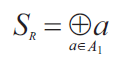

Idea techniki SAODC testowania pamięci wbudowanej, wykorzystująca charakterystykę adresową pamięci, przedstawiona została szczegółowo w [13]. Charakterystyka odniesienia (sygnatura odniesienia) SR początkowego (poprawnego) stanu pamięci definiowana jest jako suma modulo-2 adresów wszystkich komórek przechowujących wartość „1”. Prosty przykład wyliczania sygnatury odniesienia tą techniką w wypadku 2m – 1 = 23 – 1 = 7 komórek pamięci przedstawia rysunek 1.

Rys. 1. Charakterystyka adresowa SR bitowej pamięci RAM

Zgodnie z teorią testowania opartego o SAODC podczas testu analizowane są wszystkie komórki pamięci oprócz komórki o adresie 0 [13]. W zapisie bardziej formalnym powyższe podejście można przedstawić w sposób następujący. Oznaczmy pamięć bitową o liczbie komórek równej N = 2m – 1 z przestrzenią adresową A = {1, 2, 3,…, 2 m} przez M [a], a ∈ A. Niech A1: = {a ∈ A | M [a] = 1} oznacza zbiór wszystkich adresów komórek pamięci zawierających wartość „1”, a A0: = {a ∈ A | M [a] = 0} zbiór wszystkich adresów komórek pamięci zawierających wartość „0”, gdzie A1 ∪ A0 = A. Wtedy charakterystykę odniesienia SR [13] otrzymujemy poprzez zsumowanie modulo-2 wszystkich adresów z A1:

| (1) |

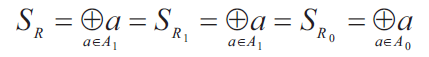

Dla powyższej charakterystyki prawdziwe są również następujące relacje:

| (2) |

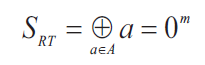

| (3) |

W tym wypadku zapis 0m oznacza sekwencję złożoną z m powtórzeń wartości 0. Używając powyższego zapisu sekwencję 000110001100011 można zapisać jako (0312)3. Z (2) wynika, iż dla pamięci o rozmiarze N = 2m – 1 charakterystyka w której sumowane są adresy wszystkich komórek z wartościami 1 jest równa charakterystyce w której sumowane są wszystkie adresy komórek z wartościami 0 (SR1 = SR0). W przykładzie z rys. 1 SR1 = 010⊕011⊕101⊕111 = 011, zaś SR0 = 001⊕100⊕110 = 011, zaś suma SR1 i SR0 zgodnie z (3) jest równa 000 (SR1⊕ SR0 = 011⊕011 = 000). Na podstawie (1) można również zdefiniować następującą własność [13]:

Właściwość 1. W technice testowania pamięci SAODC uszeregowanie adresów podczas wyliczania sygnatury SR może być przyjęte w sposób dowolny.

Wynika z niej, iż kolejność adresów sumowanych podczas wyliczania charakterystyki SR nie ma znaczenia dla końcowej wartości tej charakterystyki.

|

|

| REKLAMA |

| REKLAMA |