Zaprezentowano algorytm przygotowania systemu wieloprocesorowego oparty na procesach programowych (softcore) PicoBlaze i MicroBlaze, przeznaczony do wykonywania blokowych algorytmów kryptograficznych. Szczególna uwaga została zwrócona na sposób komunikacji między procesorami. Dokonano weryfikacji, porównania złożoności logicznej oraz wymaganego czasu na stworzenie zaprezentowanych systemów. Zaproponowane rozwiązania wykorzystane zostało do realizacji obliczeń zorganizowanych w potok, które rozbite na elementarne podprogramy wykonywane były przez poszczególne procesory. Przedstawiona została zmodyfikowana architektura mikroprocesora PicoBlaze umożliwiająca ustalenie rozmiaru pamięci programu, RAM oraz stosu.

Obecnie dostępne układy programowalne dysponują w obrębie pojedynczego układu scalonego dużą liczbą zasobów logicznych umożliwiając w ten sposób zwiększanie integracji projektowanego systemu, co wiąże się z obniżeniem kosztów i skróceniem czasu realizacji projektu. Zaistniała możliwość implementacji w ramach jednej struktury programowalnej więcej niż jednego programowego mikroprocesora, co sprzyja dalszej integracji złożonego projektu.

W artykule zaprezentowany został algorytm przygotowania systemu wieloprocesorowego w oparciu o procesory programowe (softcore) PicoBlaze i MicroBlaze, przeznaczony do wykonywania blokowych algorytmów kryptograficznych. Szczególna uwaga została zwrócona na sposób komunikacji między procesorami. Dokonano weryfikacji, porównania złożoności logicznej oraz wymaganego czasu na stworzenie zaprezentowanych systemów. Zaproponowane rozwiązania wykorzystane zostało do realizacji obliczeń zorganizowanych w potok, które rozbite na elementarne podprogramy wykonywane były przez poszczególne procesory. Przedstawiona została zmodyfikowana architektura mikroprocesora PicoBlaze umożliwiająca ustalenie rozmiaru pamięci programu,RAM oraz stosu.

W artykule przedstawiono: podstawowe założenia budowy systemu wieloprocesorowego i określone wymagania stawiane tego typu rozwiązaniom, sposób implementacji oraz wpływ przyjętych parametrów na liczbę wykorzystywanych zasobów logicznych, wyniki zaproponowanych pomiarów i ich omówienie oraz wnioski.

Realizacja systemu wieloprocesorowego w układzie programowalnym może być zorganizowana w następujący sposób:

Systemy autonomiczne pracują niezależnie od siebie, mogą być taktowane różnymi zegarami i wykorzystują różne zasoby. Nie wymagamy, aby systemy posiadały mechanizmy komunikacji wzajemnej do realizacji postawionych im zadań.

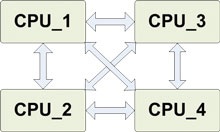

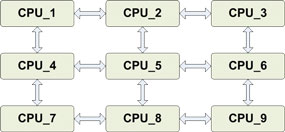

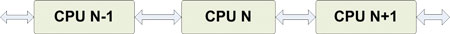

W przypadku kiedy rdzenie współpracują ze sobą wskazane jest zminimalizowanie liczby wymaganych połączeń w celu uniknięcia nadmiarowości pochłaniającej dodatkowe zasoby. Należy dostosować liczbę połączeń do realizowanego zadania przez system. Dla sieci niezupełnych pojawić może się konieczność zastosowania metod routingu i przekazywania pakietów do konkretnych procesorów. Routing zrealizowany może być sprzętowo poprzez dekodowanie adresu przez układ kombinacyjny, który zestawia odpowiednią ścieżkę lub programowo, gdzie każdy pakiet jest analizowany przez program, który decyduje o ewentualnym przekazaniu dalej pakietu. W tym przypadku przenosi się mechanizmy znane z układów NoC (Network on Chip) realizowanych w technologii ASIC do układów FPGA. Szczególną postacią jest struktura szeregowa, która umożliwia realizację algorytmów z wykorzystaniem potoku. Taka forma została przyjęta do realizacji postawionych celów. Na rysunku 1 przedstawione zostały wybrane architektury systemów wieloprocesorowych.

a) a) |  b) b) |

c) c) | |

Rys. 1. Wybrane sposoby realizacji połączeń między procesorami: a) struktura zupełna (każdy z każdym), b) sieć kratowa, c) struktura szeregowa | |

W celu komunikacji między procesorami wykorzystuje się jeden z dwóch mechanizmów, tj.: pamięć dwuportową RAM, która umożliwia jednakowy dostęp do zawartości pamięci oraz pamięć o organizacji typu FIFO (First In First Out). Pierwsze rozwiązanie obsługuje wymianę danych poprzez określoną przestrzeń adresową. Zaletą tej metody jest swobodny dostęp do dowolnej komórki pamięci. Zasadniczą wadą jest konieczność uzyskania potwierdzenia czy można nadpisać dane w niej zapamiętane umieszczone pod konkretnym adresem. Wymusza to stosowanie semaforów, które po ustawieniu blokują zapis do określonych obszarów pamięci współdzielonej. Stosowana jest najczęściej w sytuacjach, kiedy potrzebny jest dostęp swobodny do dowolnej komórki pamięci. Kolejka FIFO wymaga pojedynczego adresu w przestrzeni adresowej, dzięki czemu operacja zapisu/odczytu przebiega szybciej (nie ma potrzeby zmieniania adresu docelowego/źródłowego). Podstawowymi wadami jest brak dostępu do dowolnej komórki, konieczne jest odczytanie wcześniej zapisanych danych, oraz jednokierunkowość transmisji, co wiąże się z koniecznością podwajania liczby wymaganych zasobów w celu wzajemnej komunikacji.

Informacja o aktualizacji zawartości pamięci przekazana jest przez rejestr statusu zawierający bit ustawiany przez układ piszący do pamięci po zakończeniu procedury zapisu, kasowany przez adresata po odczytaniu danych. Do nadzoru wymiany danych między układami zastosować można jeden z dwóch mechanizmów. Pierwszy wykorzystuje wejście przerwania mikroprocesora i zapewnia minimalizację opóźnień odczytu zwalniając tym samym zajęty obszar pamięci. Wymaga on bloku sterującego przerwaniami oraz ich automatyczne kasowanie. Druga metoda polega na cyklicznym sprawdzaniu rejestru statusu (informacji o rodzaju zawartości, ważności). Zaletą wykorzystania przerwań jest przyspieszenie wymiany danych między procesorami, wiąże się to jednak z możliwością pojawienia się przestojów w wykonywaniu programu głównego. Cykliczny odczyt statusu wprowadza przestój w transmisji zmniejszając jej szybkość efektywną [1].

|

|

| REKLAMA |

| REKLAMA |